・ハーフライン読み取り後速度制御

・車線変更立ち上がりESC

・カーボン板の穴位置修正

・バッテリの組電池化

・ヒシチューブ等オヤイデ電気に発注

・ハーフライン読み取り後速度制御

・車線変更立ち上がりESC

・カーボン板の穴位置修正

・バッテリの組電池化

・ヒシチューブ等オヤイデ電気に発注

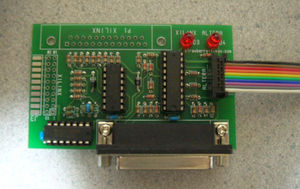

EPM7032Sデザインルールを調べたのでまとめる。

・VCCとGNDは全て接続する

・使用していないI/OピンをPin-Out Fileでしらべると”RESERVED”になっている→何処にも接続してはならない

・入力専用ピン→使わないなら、GNDに落とす

・Jtag関連(TDO)はoutput端子→何処にも接続しない

・Jtag関連(TMS,TDI,TCK)はinput端子

・TMS,TDIはTCKの立ち上がりで読み込まれる→TCKはGND

・JTAGのステートマシーンが動作しだしても、TMS=1ならIdle状態に戻る→TMSはVCC

・グローバルクロック→そのままクロックを繋ぐ

・グローバルリセット(LOWレベルでFFをリセット)→プルアップ処理

・出力イネーブル専用ピン(Lowレベルで動作)→GND

・Jtag書き込み中の端子は50kΩでプルアップされる。

質問

・上ではJtag関連端子を処理しようとしていますが、Jtagピンを開放のまま(or TCKだけGND)にすることにより、使用上問題は発生するのでしょうか?

参照

Pin-Out File

JTAG のテクニカルガイド:http://www.xjtag.com/jp/support-jtag/jtag-technical-guide.php

アルテラ・デバイスの使用上の注意:http://www.altera.co.jp/literature/ds/dsoprq_j.pdf

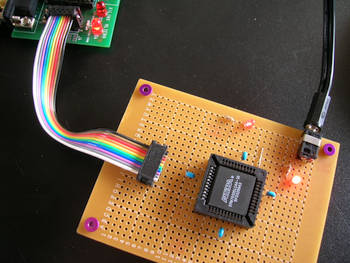

CPLD周辺回路を仕上げ書き込みの確認をした。

途中でJtagの結線ミスによりツマズク。原因は、だいぶ以前に書いた結線図。

作業前に以前の作業内容のチェックが必要である。

・Quartus II Web Editionのライセンス再取得

・次は、クロック信号を使ってLED点滅をする

・樹脂パーツ切り出し

・CPLD周辺部分若干進行

・メイン基板アートワーク若干進行

次はCPLD周辺部分

///////////////////////////

メイン基板のアートワークを進める。

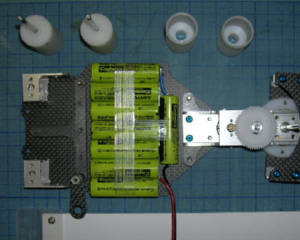

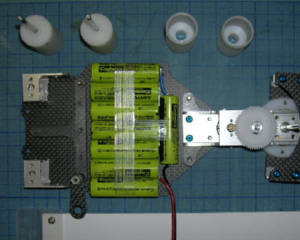

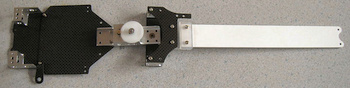

支援のもとメカの加工が進む。

形になっている部品だけでも仮組みして、モチベーションを上げる。

////////////////////////////

1mm厚カーボン板の剥離が激しい。

カーボン板自体の強度は十分だが、

120番の紙やすりで外形を削ると、表面の繊維が剥れる。

同メーカの2mm厚品だと剥離は起きない。こういう物なのだろうか。

1.スーパーラジコンでピニオンギヤを購入

2.F-Shop!に発注

・EPM7032SLC44-15

・PLCCソケット

・PLCC引抜工具

3.ストロベリー・リナックスに発注

・PLD-PGMキット

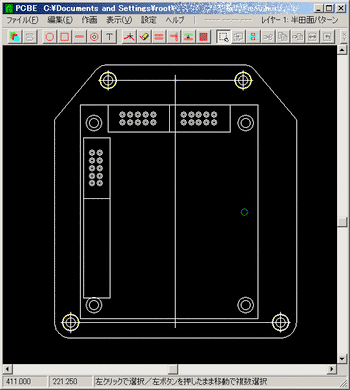

メイン基板の外形を描く。

面積は前モデルと同程度、乗せる回路は数割増し。

ToDo

・CPUボードCLK端子の座標計測

・CPLD開発環境構築